導(dǎo)航

微信

頂部

news center

發(fā)布時(shí)間:2023-11-17 閱讀: 來(lái)源:管理員

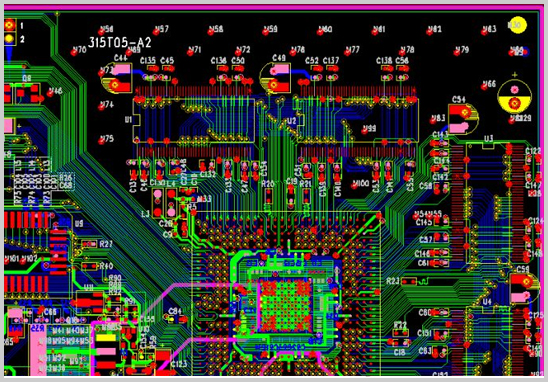

高速PCB設(shè)計(jì)涉及的布線技巧和注意事項(xiàng)較多,其中一些關(guān)鍵方面包括信號(hào)完整性、阻抗匹配、電磁兼容性和功耗。深圳宏力捷電子是專(zhuān)業(yè)PCB設(shè)計(jì)公司,可承接多層、高精密/BGA封裝以及盲孔/埋孔的PCB設(shè)計(jì)畫(huà)板服務(wù),接下來(lái)為大家介紹一些高速PCB設(shè)計(jì)的布線技巧。

1. 層次規(guī)劃: 使用多層PCB板并合理規(guī)劃層次。分層設(shè)計(jì)可以提供更多的布線空間,同時(shí)減小信號(hào)回傳路徑,降低串?dāng)_。

2. 差分對(duì): 對(duì)于高速信號(hào),使用差分對(duì)可以提高信號(hào)完整性,降低串?dāng)_。確保差分對(duì)的布線長(zhǎng)度一致,差分對(duì)之間的間距適中。

3. 阻抗匹配: 針對(duì)高速信號(hào)線,保持適當(dāng)?shù)淖杩蛊ヅ浞浅V匾J褂煤线m的 PCB 材料、規(guī)范的線寬和間距,以確保所需的阻抗。

4. 信號(hào)層與電源/地層隔離: 將信號(hào)層與電源/地層分隔開(kāi),減小信號(hào)回流路徑,降低串?dāng)_。同時(shí),確保電源和地的布線寬度足夠,以降低電阻。

5. 最短路徑和直角避免: 盡量確保信號(hào)線的最短路徑,避免使用直角折線,因?yàn)橹苯菚?huì)引起信號(hào)反射和阻抗不匹配。

6. 差分匹配和單端匹配: 如果可能,將單端信號(hào)轉(zhuǎn)換為差分信號(hào)以提高抗干擾能力。如果必須使用單端信號(hào),請(qǐng)確保相鄰的信號(hào)線保持足夠的間距,以降低串?dāng)_。

7. 電磁兼容性(EMC): 采用地孔、電源平面、濾波器等技術(shù)來(lái)提高電磁兼容性,減小輻射和敏感性。

8. 電源噪聲過(guò)濾: 在電源引腳和電源平面之間使用適當(dāng)?shù)碾娫丛肼暈V波器,以減小電源噪聲對(duì)信號(hào)的影響。

9. 差分對(duì)長(zhǎng)度匹配: 盡量確保差分對(duì)的長(zhǎng)度匹配,以防止相位差引起的信號(hào)失真。

10. 緩沖器和驅(qū)動(dòng)器: 在需要時(shí)使用緩沖器和驅(qū)動(dòng)器來(lái)增強(qiáng)信號(hào)強(qiáng)度,降低傳輸延遲。

在進(jìn)行高速PCB設(shè)計(jì)時(shí),最好參考相關(guān)的設(shè)計(jì)規(guī)范和標(biāo)準(zhǔn),并利用仿真工具來(lái)驗(yàn)證設(shè)計(jì)的性能,以確保信號(hào)完整性和可靠性。

獲取報(bào)價(jià)